日立製作所が量子コンピューター実現へのブレークスルー達成

シリコンベースで量子ビット開発に成功、コヒーレンス時間を2ケタ向上

2005.08.20−日立製作所は19日、日立ヨーロッパの日立ケンブリッジ研究所が英ケンブリッジ大学と共同で、量子コンピューター実現へ向けての重要なブレークスルーを達成したと発表した。計算素子となる量子ビット(二重量子ドット)を、シリコン技術を利用して開発することに世界で初めて成功したことに加え、ガリウムヒ素などの他の半導体材料で報告されているよりも2ケタ大きな約200ナノ秒というコヒーレンス時間を実現できた。研究グループは今後、複数の量子ビットの制御やアルゴリズム演算の実行などへと研究を進めていくが、シリコンという標準的な半導体プロセスを利用することができるため、実用化へ向けて最も有利なポジションにつけたとしている。

量子コンピューターは、量子力学の重ね合わせの原理を使って超並列計算を実現するもので、その演算器を量子ビットと呼ぶ。量子力学の法則によって、量子ビットは0と1の状態を同時に実現しているため、n個の量子ビットを用意すれば2のn乗個の状態が同時に実現されることになる。それを“量子もつれ合い”という量子力学固有の性質を利用して一括処理することにより、1回のステップで2のn乗回の計算が可能。処理能力は量子ビットの数に応じて指数関数的に増加する。このようにして、現在のコンピューターとはケタ違いの性能を発揮できると期待されている。

量子コンピューターは、量子力学の重ね合わせの原理を使って超並列計算を実現するもので、その演算器を量子ビットと呼ぶ。量子力学の法則によって、量子ビットは0と1の状態を同時に実現しているため、n個の量子ビットを用意すれば2のn乗個の状態が同時に実現されることになる。それを“量子もつれ合い”という量子力学固有の性質を利用して一括処理することにより、1回のステップで2のn乗回の計算が可能。処理能力は量子ビットの数に応じて指数関数的に増加する。このようにして、現在のコンピューターとはケタ違いの性能を発揮できると期待されている。

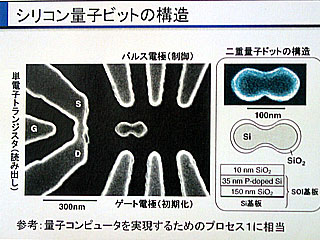

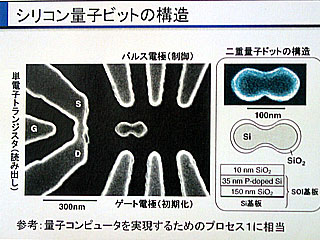

今回開発に成功したシリコン量子ビット(写真)は、電子を閉じ込めた量子ドットを2つくっつけたひょうたん型の構造(二重量子ドット)で、両側に電極を配置して、信号を単電子トランジスターで読み出す仕組み。量子ビット自体の大きさは150ナノメートル×50ナノメートルで、全体が酸化膜で覆われているのが特徴となる。まず、ゲート電極を作用させて電子を片側に寄せて局在化(0か1の状態)させ、次にパルス電極からコヒーレンス振動を送って左右の電位差をなくし、電子が非局在の重ね合わせ状態(0と1が同時に存在する状態)をつくりだす。

外乱要因となる配線が存在しないため、量子ビットの重ね合わせ状態が壊れにくく、結果としてコヒーレンス時間を長くすることができる。この点で、シリコンがもともとの材料の性質として量子状態を壊しにくいことに加え、今回の量子ビットを覆っている酸化膜がインシュレーターとなって振動が伝わりにくいため、コヒーレンス時間の大きな向上につながったということだ。

量子コンピューターでは、重ね合わせ状態が持続するコヒーレンス時間内に計算処理を行うため、これが長いほど十分な計算ステップが確保できることになる。ただ、コヒーレンス時間は超伝導ジョセフソン接合電荷素子で5ナノ秒、ガリウムヒ素系半導体の二重量子ドットで1ナノ秒までの実績しか出ていなかった。今回のシリコン量子ビットで実現したコヒーレンス時間200ナノ秒は、パルス電極からメガヘルツ帯域のパルスをかけ、最初の振幅が半減するまでの時間を観測したもの。ギガヘルツ帯域のパルスを利用すれば、200ナノ秒という時間は実用化の目安といわれる1万ステップの計算ができる時間的余裕に相当するという。将来的には、コヒーレンス時間自体を5倍に延長できるともしている。

日立によると、量子コンピューター実現までのプロセスは4段階あり、(1)単一量子ビットによる重ね合わせ状態の制御、(2)2つの量子ビットによる制御NOTゲート(ロジック単位であるゲートを働かせる)、(3)多数の量子ビットによるアルゴリズム演算、(4)量子ビットのLSI化による実戦的アルゴリズム演算−に分かれるという。

その意味で、今回の研究は第1段階ではあるが、第4段階にいたるプロセスをにらんだ有望性で他の研究グループをリードしているというのが同社の見方である。大きなポイントはやはりコヒーレンス時間の長さだが、第3・第4段階に向けてはシリコンベースであるという特徴がさらに重要性を帯びる。(別表参照)

とくに、単電子トランジスターの特性を生かした容量接合の無配線構造が可能なため、多数の量子ビットを配列して二次元アレイ化することで、比較的容易にLSI化を図ることができるのである。当面は、100個から1万個の量子ビットを集積することが目標になるという。

日立では、第2段階に当たる制御NOTゲートの実現を1年以内に達成したあと、第3段階以降のステージへと研究を進める考え。量子コンピューターは数10年後に実用化する技術だといわれているが、シリコンをベースにすることでその実現時期を大幅に早めることができるとしている。

量子コンピューターでは、ソフトウエアのアルゴリズムも現在のコンピューターとは大きく異なることになるが、大規模な遺伝子解析や分子モデル計算、材料設計、暗号解読や複雑な暗号化、難解な量子力学の解析などのアプリケーションが期待されているようだ。

量子ビットの実現方法

資料:日立製作所

| 量子ビットの生成方法 |

生成条件 |

コヒーレンス時間 |

実現ステップ |

LSI化 |

| イオントラップ |

超高真空、極低温 |

非常に長い |

第2段階(制御NOTゲート、4量子ビットも作製) |

困難 |

| NMR(核磁気共鳴) |

溶液中 |

長い |

第3段階(7量子ビット、15の素因数分解) |

不可能 |

| 超伝導ジョセフソン接合電荷素子 |

固体素子、極低温 |

〜5ns |

第2段階(制御NOTゲート) |

有望 |

| GaAs系半導体二重量子ドット |

固体素子、極低温 |

〜1ns |

第1段階(コヒーレンス制御) |

有望 |

| シリコン半導体二重量子ドット |

固体素子、極低温 |

200ns |

第1段階(コヒーレンス制御) |

とくに有望 |

量子コンピューターは、量子力学の重ね合わせの原理を使って超並列計算を実現するもので、その演算器を量子ビットと呼ぶ。量子力学の法則によって、量子ビットは0と1の状態を同時に実現しているため、n個の量子ビットを用意すれば2のn乗個の状態が同時に実現されることになる。それを“量子もつれ合い”という量子力学固有の性質を利用して一括処理することにより、1回のステップで2のn乗回の計算が可能。処理能力は量子ビットの数に応じて指数関数的に増加する。このようにして、現在のコンピューターとはケタ違いの性能を発揮できると期待されている。

量子コンピューターは、量子力学の重ね合わせの原理を使って超並列計算を実現するもので、その演算器を量子ビットと呼ぶ。量子力学の法則によって、量子ビットは0と1の状態を同時に実現しているため、n個の量子ビットを用意すれば2のn乗個の状態が同時に実現されることになる。それを“量子もつれ合い”という量子力学固有の性質を利用して一括処理することにより、1回のステップで2のn乗回の計算が可能。処理能力は量子ビットの数に応じて指数関数的に増加する。このようにして、現在のコンピューターとはケタ違いの性能を発揮できると期待されている。